全球記憶體產業已進入一個必須尋求新興替代技術的時代。在多樣化的次世代記憶體技術中,為何電阻式記憶體,在類神經仿生運算的應用上值得期待?其更被業界認為是最有機會成為下世代通用記憶體的選擇,同時也是目前投入研發廠商最多之技術?

邁入尋求全新嵌入式非揮發性記憶體技術的時代

近年來由於物聯網、行動裝置、高速電腦和智慧汽車等產業的快速發展,大幅推升了人工智慧(AI)及邊緣計算(Edge Computing)等巨量運算架構的應用需求,也因此既有高容量存儲元件例如 DRAM 及 NAND Flash,其在耗電量及資料存取速度上已無法跟上需求的腳步。

並且,隨著半導體製程線寬縮微已超越 14nm、電晶體發展主流遷移到 FinFET 或 GAA 等先進結構,長期應用於 CMOS 晶片上存儲的嵌入式 NOR Flash 礙於「快閃記憶體縮放限製(Flash Memory Scaling Limit)」問題,也已無法跟上 SoC 晶片整合製程的發展要求,必須要有全新的嵌入式非揮發性記憶體技術,才能搭配下一世代以先進製程所製造的 ASIC 和 MCU。

電阻式記憶體為何備受期待?

過去數十年來在世界各國合力開發下,已初略成形的次世代非揮發性記憶體技術包括鐵電記憶體(FRAM)、相變化記憶體(PRAM)、磁阻式記憶體(MRAM)、以及電阻式記憶體(RRAM)等。這些候選的新興技術,不僅讀寫速度都比 NAND Flash 要快 1,000 倍以上,並且皆能夠在奈安培(nA)的極低電流下操作。同時,也都具有潛力可突破範紐曼(von Neumann)架構瓶頸,實現記憶體內運算(In-memory Computing)之能力。

在多樣化的次世代記憶體技術中,電阻式記憶體由於相對具有讀寫快速、低耗能、結構簡單、資料儲存時間長、重複操作可靠度佳與成本便宜等產品優勢,以及適合應用於類神經仿生運算的電導(電阻)漸變類比特性,被業界認為是最有機會成為下世代通用記憶體的選擇,同時也是目前投入研發廠商最多之技術,包含 Adesto(2020 年已被 Dialog 併購)、Crossbar、Samsung、Panasonic、Micron、Hynix 及 Intel 等公司,都各別擁有不同的電阻式記憶體技術。

電阻式記憶體由來

電阻式記憶體(Resistive Random Access Memory, RRAM)結構為簡單的金屬-絕緣層-金屬(Metal-Insulator-Metal, MIM),其原理為施予電壓或電流操作,利用物質電阻改變元件的高低電阻狀態,達成數位訊號儲存效果。

電阻式記憶體最早起源自 1960 年代,研究學者 Hickmott 發現氧化鋁(AlOx)材料經過電壓或電流操作後,其電阻狀態會因此改變 [1];近年來,研究發現氧化鎳(NiO)[2-5]、氧化鈦(TiOx)[6-9]、氧化鉿(HfOx)[10-13] 等絕緣體材料,亦可用於 RRAM 的中間絕緣層。RRAM 可利用特定的電壓來讀取不同狀態的電阻值(電流值),進而判讀元件「1」和「0」的邏輯狀態。此外,RRAM 具有良好的非揮發性記憶特性,其訊號儲存狀態可在不施加外在偏壓的情況下,保存至下一次訊號的寫入或抹除。

RRAM 物理機製與操作特性

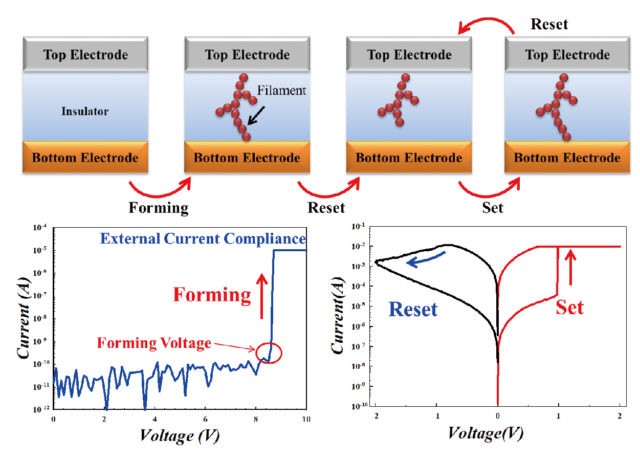

RRAM 的物理機製目前較受到注目的是燈絲理論(Filament Theory)[14-16],普遍認為 RRAM 的操作方式是在一開始時給予元件一較大的外加偏壓,使氧化物絕緣層內部形成導通路徑,此時絕緣層會變為低阻態(Low Resistance State, LRS),此過程通常需要限製電流(Compliance Current),避免電流過大反應劇烈使元件永久崩潰,此步驟稱之為 Forming。

接著以元件偏壓控製氧離子與氧空缺複合,使導通路徑阻斷,進而從低電阻態(LRS)回到高電阻態(High Resistance State, HRS),此過程稱為 Reset;而再次給予小於 Forming 所需的電壓,即可將阻斷的導通路徑重新連接,從高阻態(HRS)再次回到低阻態(LRS),此步驟稱為 Set。

來回操作 Set 與 Reset process 就可以達成 RRAM 的寫入與抹除,RRAM 的操作流程如圖 1 所示,而在讀取方麵主要是藉由一微小的讀取電壓來判讀不同的電阻值,以分辨數位訊號 0 和 1(圖 2)。RRAM 依阻值狀態變化的不同可區分為阻絲型與介麵型,阻絲型 RRAM 即於上下兩電極間有一連續傳導路徑(圖 3),也是目前 RRAM 在傳導機製中較受到廣泛認同的類型;另一為介麵型 RRAM(圖4),透過施加外部電壓,使絕緣體層中形成氧空缺或載子電荷進行電子傳遞使其阻態改變,當氧空缺或載子電荷變多,其電流增大,因此元件電極間的絕緣體層麵積大小會影響阻態變化。

▲圖 1 RRAM 切換流程與電性輸出圖

詳文請至 http://www.aimniche.com/ 全文續閱 相關課程資訊:https://is.gd/uWxCJE

創新風格測評網

創新風格測評網